### (Pfl

NetChip: A Design Flow for Networks on Chips

Stergios Stergiou

Stanford University, CA, USA

Motivation

xpipes Lite Library Architecture

NetChip Design Flow

Experimental Results

•Design Complexity:

•From 10 to 100+ Cores!

•Performance:

•Requirements Go Up!

•Power Budget Remains Fixed

•Scalability:

•Current Architectures Cannot Keep Up!

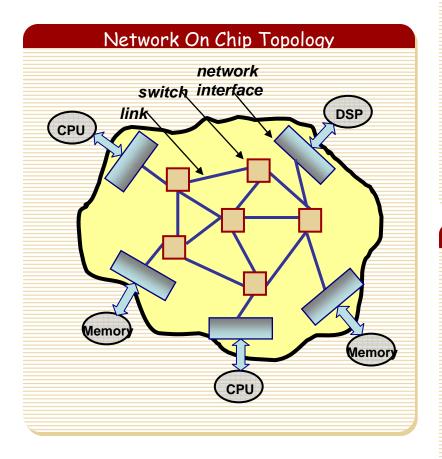

IntroductionMotivationxpipes Lite ArchitectureTraditional Bus ArchitecturesDesign FlowNoCs

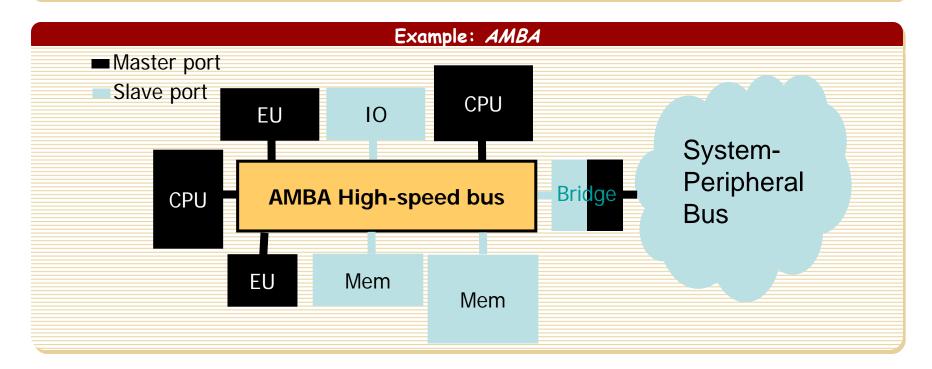

#### **Bus Architectures**

Sonics MicroNetwork

•Highly Parameterizable, TDMA-based Bus

•STBus / AMBA

•High Performance, Support Instantiation of Various Topologies

Protocol Lacks parallelism • Traditionally: oin order completion ono multiple outstanding transactions High arbitration overhead •Bus architecture exposed •Hinders IP integration Topology •Scalability limitation of shared bus solution

Crossbar

Routing & Flow Control

| Previous Work                                |

|----------------------------------------------|

| •NoC Architectures                           |

| OSPIN, DATE'OO                               |

| •Dally & Towles, DAC'01                      |

| •Aethereal, DATE'03                          |

| •xpipes, ICCD'03                             |

| Design Tools                                 |

| •Power Analysis: T. Ye et al, DAC'02         |

| •xpipes Compiler: A. Jalabert et al, DATE'04 |

| oIndustry                                    |

| Arteris, STmicroelectronics                  |

| Xpipes Lite                              |

|------------------------------------------|

| Second xpipes Design Library Version     |

| •Complete Redesign!                      |

| •Goals:                                  |

| <ul> <li>High Performance</li> </ul>     |

| Automated Synthesis                      |

| •Comparison With Original xpipes Library |

| •Lower Latency (7 to 2 stage switches)   |

| •Fully Synthesizable!                    |

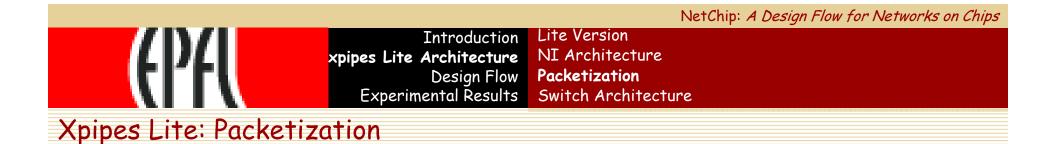

Introduction Lite Version xpipes Lite Architecture Design Flow Packetization Experimental Results Switch Architecture

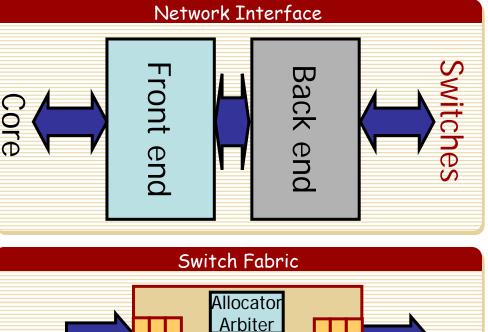

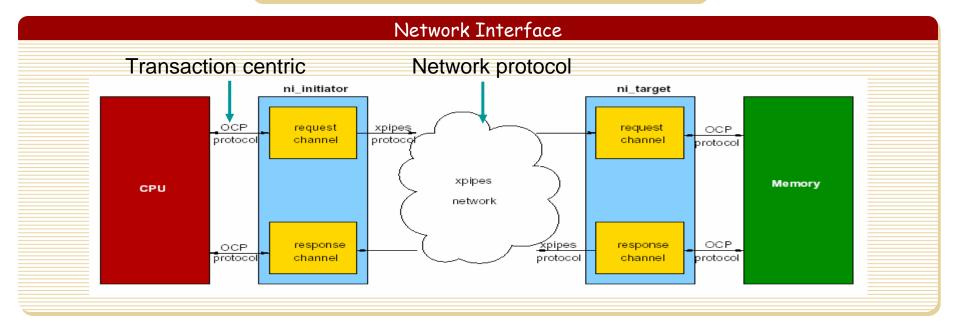

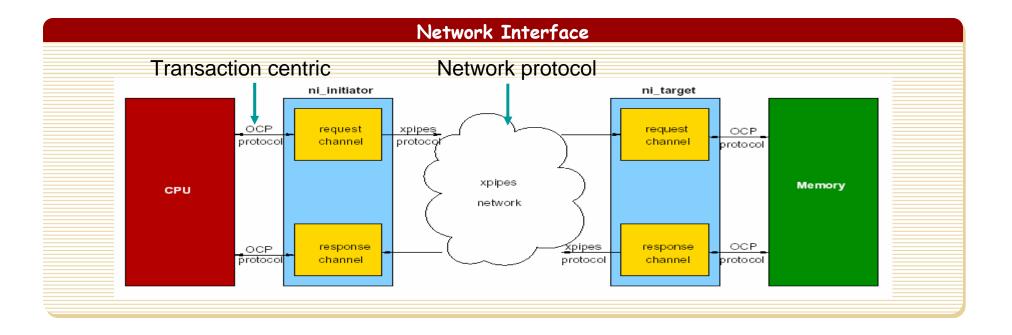

#### **Xpipes Lite: Network Interface**

#### OCP

End-to-end communication protocol

Independent request/response

Can be tailored to core features

Support for sideband signals

ointerrupts

Efficient burst handling

Supports threading extensions

Introduction Lite Version xpipes Lite Architecture Design Flow Experimental Results Switch Architecture

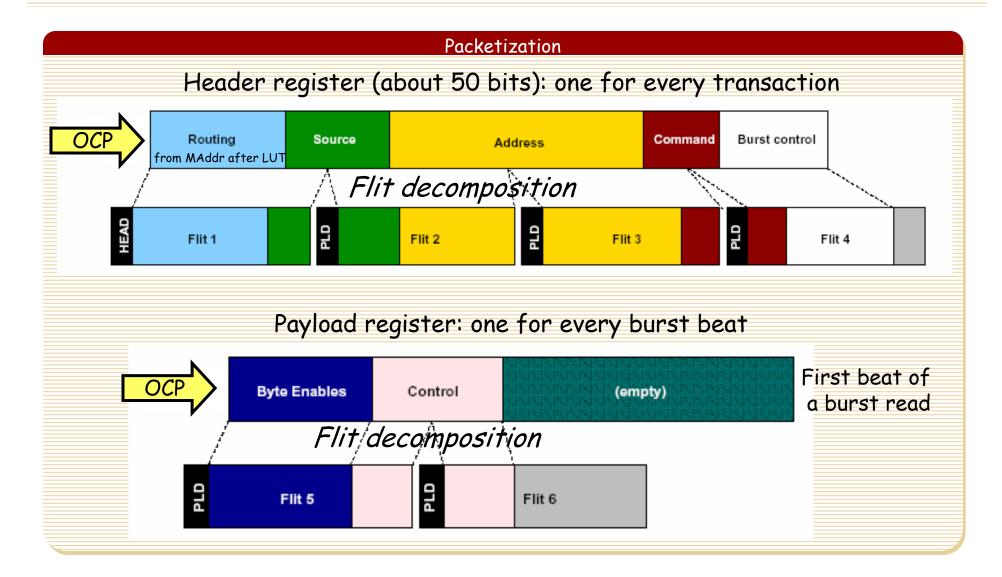

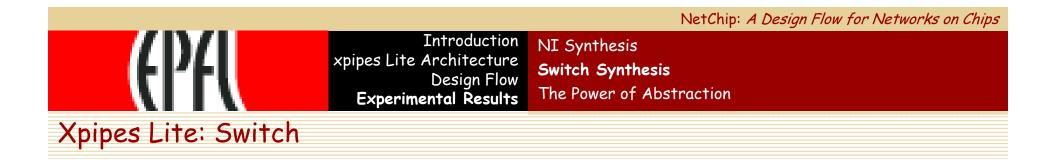

#### Xpipes Lite: Switch

Output Queued

Buffering for Performance

ACK/nACK Flow & Error Control

•Support for Asymmetric Topologies

•Designed for Pipelined, Unreliable Links

- •ACK/nACK Flow & Error Control

- •2-stage pipelined

- •High Speed (1GHz @ 130nm)

- •Wormhole Switching

- •Arbitration: Fixed / RR

- •Source Based Routing

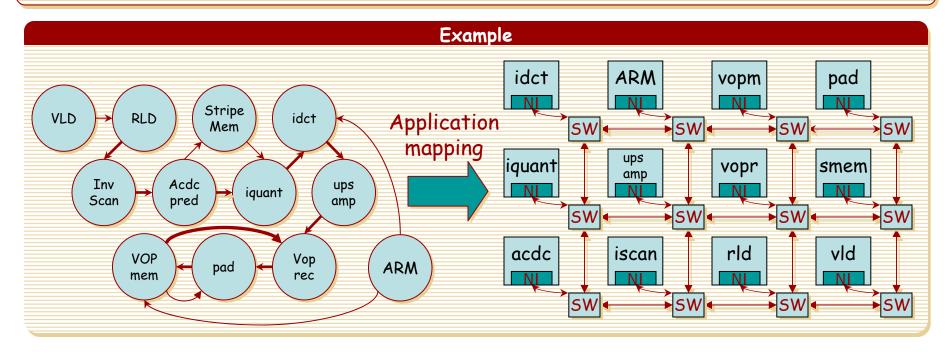

Introduction xpipes Lite Architecture **Design Flow** Experimental Results **High Level View** NoC Synthesis Flow Topology Instantiation

### High Level View

#### Typical SoC Application Characteristics

•Complex

- Highly Heterogeneous

- •Communication Intensive

•xpipes: Synthesizable, High Performance, Heterogeneous NoC Infrastructure

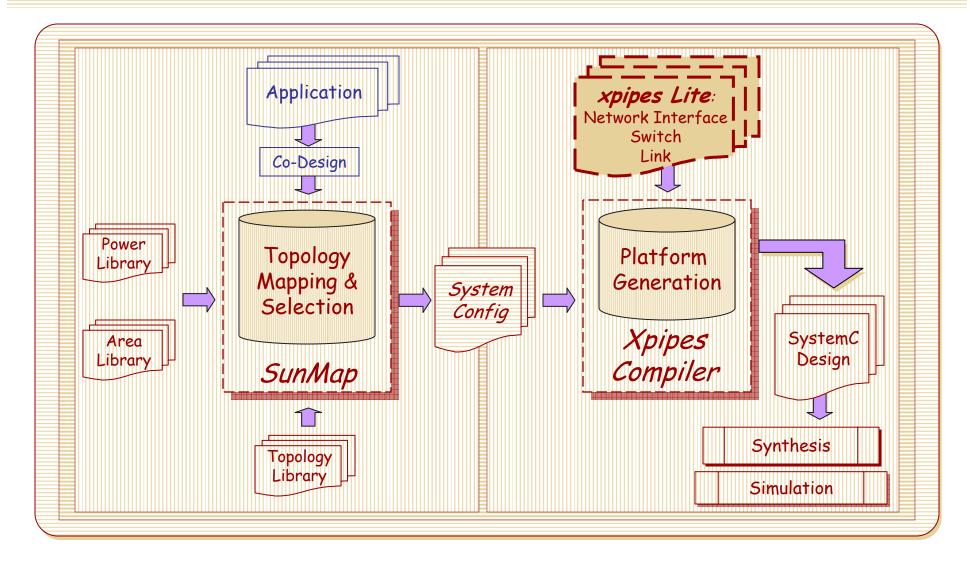

#### NetChip NoC Synthesis Flow

Introduction xpipes Lite Architecture **Design Flow** Experimental Results High Level View NoC Synthesis Flow **Topology Instantiation**

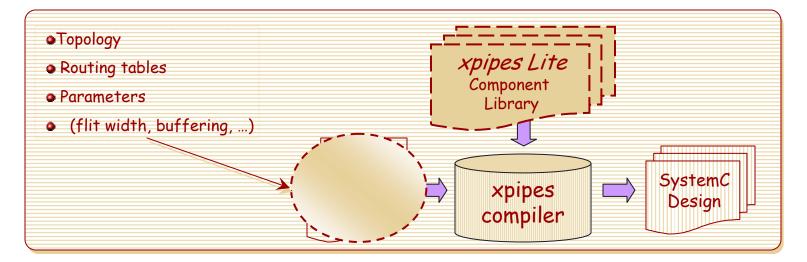

Topology Instantiation

#### xpipes Compiler

•Creates a Class Template For Each Network Component Type

- Component Optimizations

- •I/O Ports

- Buffer Sizes

- Hierarchical System Instantiation

- Synthesis View

- Simulation View

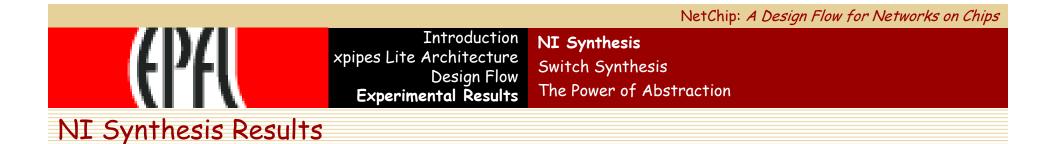

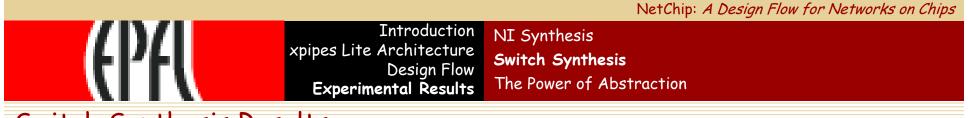

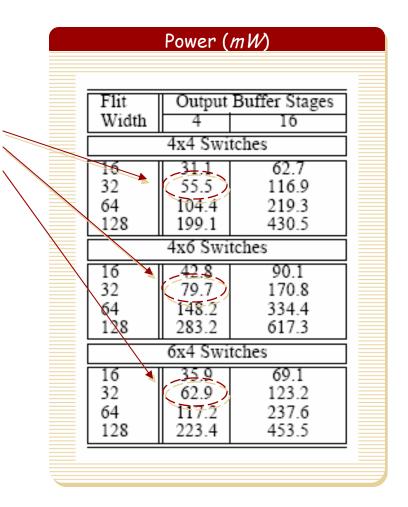

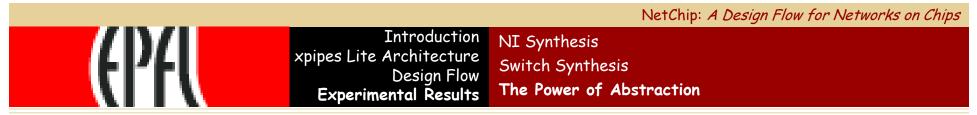

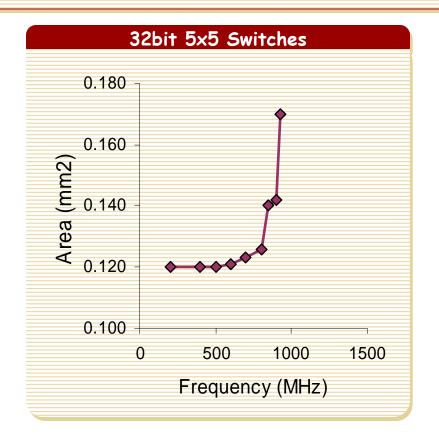

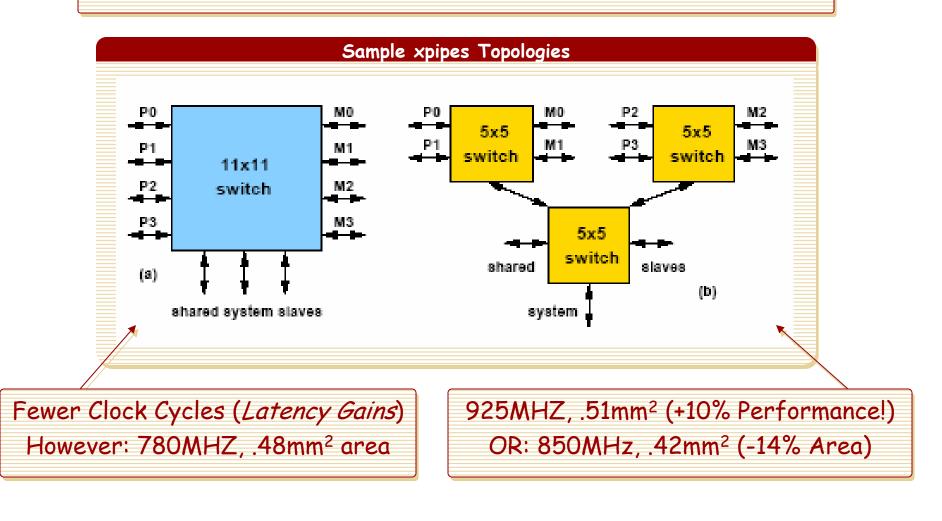

#### Switch Synthesis Results

Area Breakdown & Mesh Case Study

A 3x4 xpipes mesh for 4 processors and 7 slaves occupies ~2,2 mm<sup>2</sup>

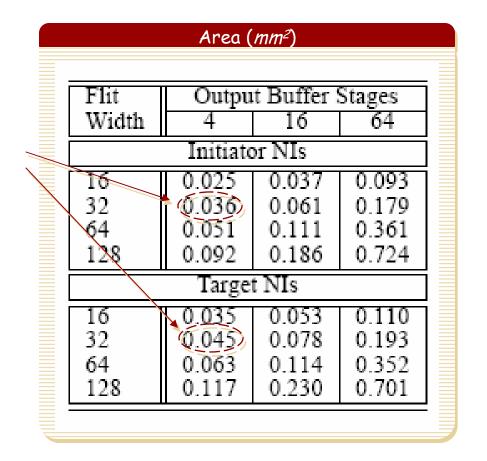

Initiator NI / Target NI / 4x4 Switch @ 1GHZ

6x4 Switch @ 875 - 980 MHz

•Greater Opportunity for Optimization

•Various Power/Frequency/Area Tradeoffs!

The Power of Abstraction: Shift Efforts at a Higher Abstraction Layer

Quick and Accurate Estimations

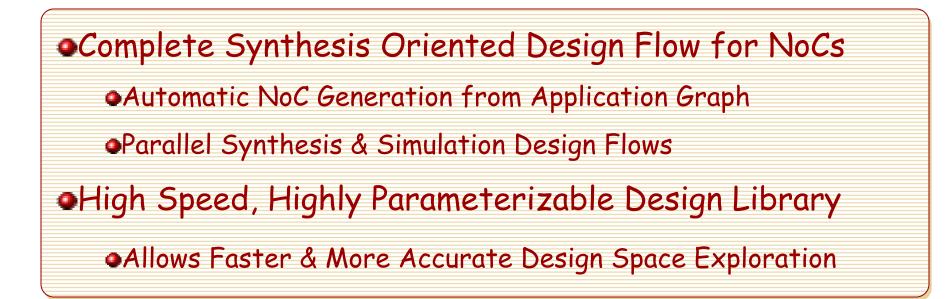

# Conclusion

(PA)

## Thank You!

(FP)

Stergios Stergiou

Stanford University, CA, USA